Return to list

Previously, we told of the benefits our fellows in the semiconductor industry can harvest by adopting the principles of an Enterprise Architecture (EA) Program. We brought to light that – though the time and effort to fire up SemiConductor EA seems counter-productive – the fruits of a lowered infrastructure spend, as well as a leap forward in the race to tape out are the rewards. EA Programs are going to prove to the industry that those who step up will step away from the crowd.

The technology stack supporting design underpins this modern approach to super-computing and must abandon the stovepipe and the skunk-works. The narrow-minded architecture is costly. The holistic approach to High Performance Computing (HPC) design encompassing; storage, servers, virtualization, connectivity and cloud pushing up through the capture, design, simulation and verification applications needs to be established throughout the flow. An optimized stack yields the performance you want.

The benefits of enterprise-class technology may not be so obvious, but the value is quantified as consumption of the resources grows. As the demand grows, first step is often to eliminate slowdowns with immediate point solutions, which may not fit into an integrated EA topology. These short sighted solutions often solve department-centric challenges, yet these short-sighted answers result in higher costs overall. The real cost is support of the disparate systems, and effort to integrate.

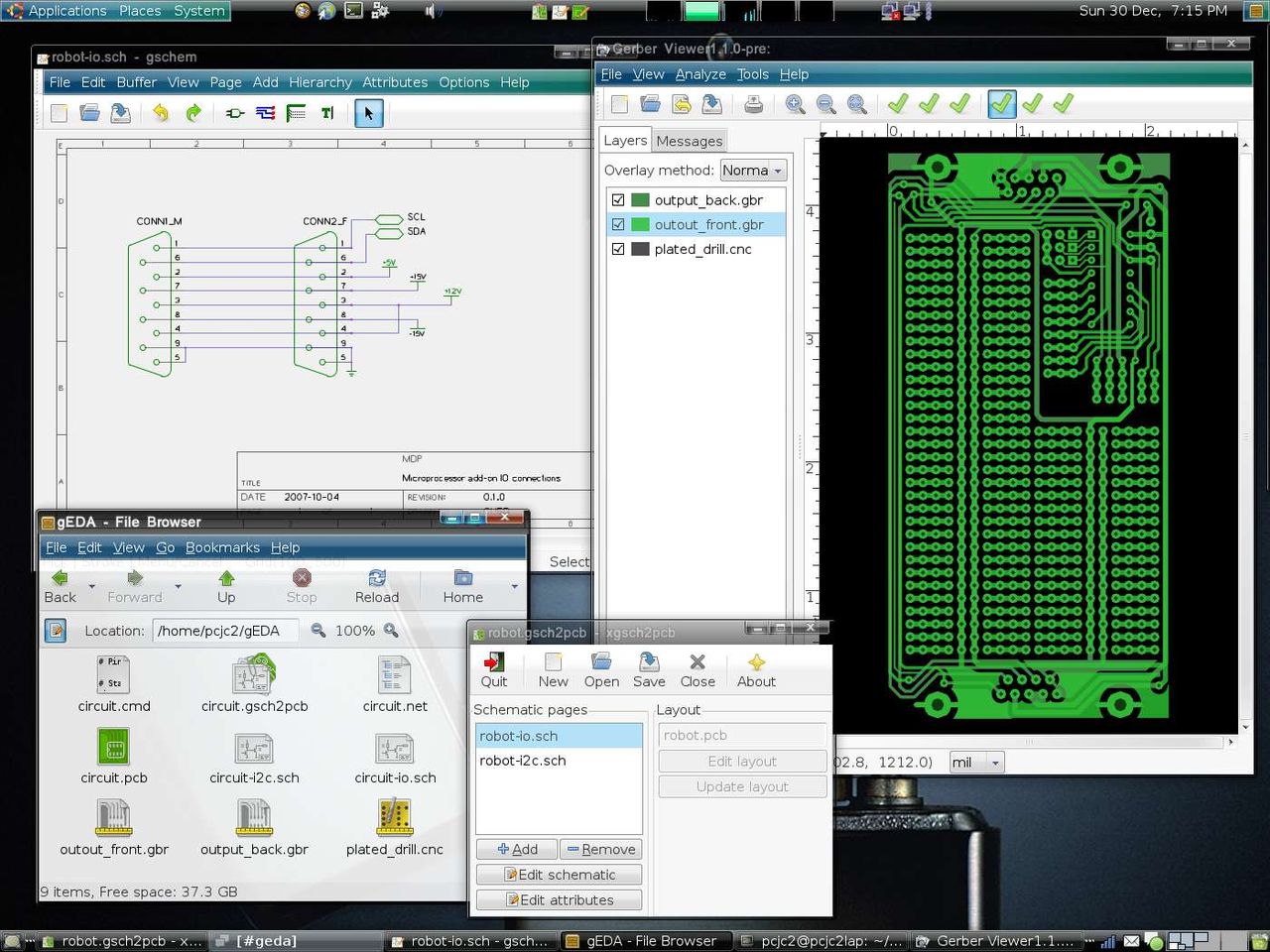

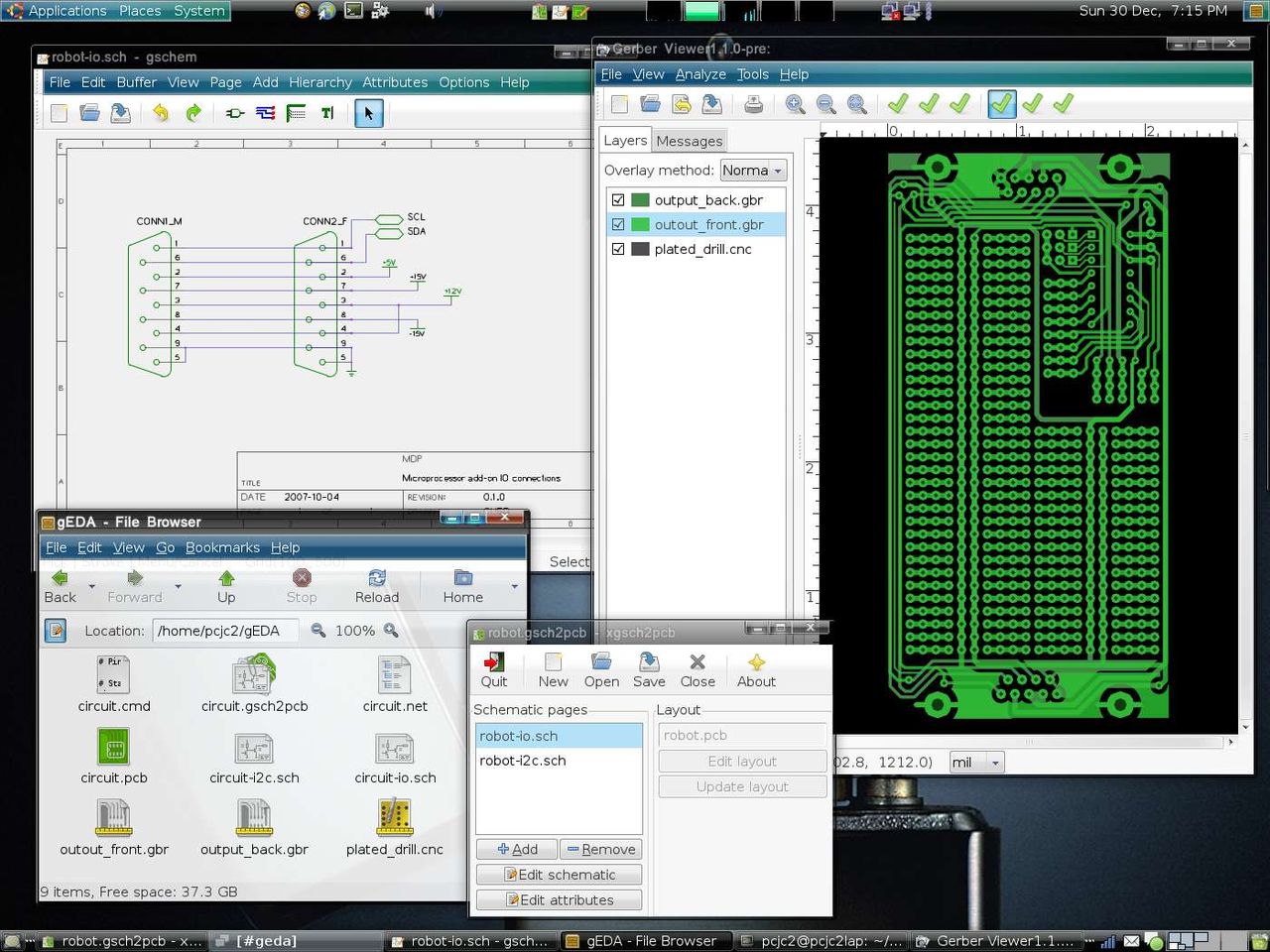

All too often, a design firm’s EDA tools support team has the laborious job of maintaining several hundred integration patterns and the RTL developer is continually adding another nightly batch job – these end up being the tape and strapping wire that is cobbled together to create a synthetic alternative to an Enterprise-class environment. The environment starts to resemble a modern-day Rube Goldberg machine.

One example is we looked at a combination Semiconductor design/Analysis environment for a medical device manufacturer. Taking the holistic approach we shaved 40 % off the $ 3 million allocated budget, saved $ 550k in manpower costs and were able to increase analysis coverage by 20 %. So, as the industry pursues 10 nanometer solutions, those design firms that have tooled their compute environment effectively with an Enterprise-class topology will be the ones who will be able to start and end their design lifecycle without having to ask their supply chain team, their HR team, and their integration team to throw a king’s ransom at the problem. Transition the skunk works, apply EA to modernize your infrastructure on a achievable schedule may prove a tough challenge. Etarios can guide you with as much or as little help as you’d like. Please check out https://www.etairos.com to see what Etairos can do for you!

Previously, we told of the benefits our fellows in the semiconductor industry can harvest by adopting the principles of an Enterprise Architecture (EA) Program. We brought to light that – though the time and effort to fire up SemiConductor EA seems counter-productive – the fruits of a lowered infrastructure spend, as well as a leap forward in the race to tape out are the rewards. EA Programs are going to prove to the industry that those who step up will step away from the crowd.

The technology stack supporting design underpins this modern approach to super-computing and must abandon the stovepipe and the skunk-works. The narrow-minded architecture is costly. The holistic approach to High Performance Computing (HPC) design encompassing; storage, servers, virtualization, connectivity and cloud pushing up through the capture, design, simulation and verification applications needs to be established throughout the flow. An optimized stack yields the performance you want.

The benefits of enterprise-class technology may not be so obvious, but the value is quantified as consumption of the resources grows. As the demand grows, first step is often to eliminate slowdowns with immediate point solutions, which may not fit into an integrated EA topology. These short sighted solutions often solve department-centric challenges, yet these short-sighted answers result in higher costs overall. The real cost is support of the disparate systems, and effort to integrate.

All too often, a design firm’s EDA tools support team has the laborious job of maintaining several hundred integration patterns and the RTL developer is continually adding another nightly batch job – these end up being the tape and strapping wire that is cobbled together to create a synthetic alternative to an Enterprise-class environment. The environment starts to resemble a modern-day Rube Goldberg machine.

One example is we looked at a combination Semiconductor design/Analysis environment for a medical device manufacturer. Taking the holistic approach we shaved 40 % off the $ 3 million allocated budget, saved $ 550k in manpower costs and were able to increase analysis coverage by 20 %. So, as the industry pursues 10 nanometer solutions, those design firms that have tooled their compute environment effectively with an Enterprise-class topology will be the ones who will be able to start and end their design lifecycle without having to ask their supply chain team, their HR team, and their integration team to throw a king’s ransom at the problem. Transition the skunk works, apply EA to modernize your infrastructure on a achievable schedule may prove a tough challenge. Etarios can guide you with as much or as little help as you’d like. Please check out https://www.etairos.com to see what Etairos can do for you!

Accelerate your design lifecycle by applying Enterprise-class Architecture

Ron Smith / September 19, 2015

Previously, we told of the benefits our fellows in the semiconductor industry can harvest by adopting the principles of an Enterprise Architecture (EA) Program. We brought to light that – though the time and effort to fire up SemiConductor EA seems counter-productive – the fruits of a lowered infrastructure spend, as well as a leap forward in the race to tape out are the rewards. EA Programs are going to prove to the industry that those who step up will step away from the crowd.

The technology stack supporting design underpins this modern approach to super-computing and must abandon the stovepipe and the skunk-works. The narrow-minded architecture is costly. The holistic approach to High Performance Computing (HPC) design encompassing; storage, servers, virtualization, connectivity and cloud pushing up through the capture, design, simulation and verification applications needs to be established throughout the flow. An optimized stack yields the performance you want.

The benefits of enterprise-class technology may not be so obvious, but the value is quantified as consumption of the resources grows. As the demand grows, first step is often to eliminate slowdowns with immediate point solutions, which may not fit into an integrated EA topology. These short sighted solutions often solve department-centric challenges, yet these short-sighted answers result in higher costs overall. The real cost is support of the disparate systems, and effort to integrate.

All too often, a design firm’s EDA tools support team has the laborious job of maintaining several hundred integration patterns and the RTL developer is continually adding another nightly batch job – these end up being the tape and strapping wire that is cobbled together to create a synthetic alternative to an Enterprise-class environment. The environment starts to resemble a modern-day Rube Goldberg machine.

One example is we looked at a combination Semiconductor design/Analysis environment for a medical device manufacturer. Taking the holistic approach we shaved 40 % off the $ 3 million allocated budget, saved $ 550k in manpower costs and were able to increase analysis coverage by 20 %. So, as the industry pursues 10 nanometer solutions, those design firms that have tooled their compute environment effectively with an Enterprise-class topology will be the ones who will be able to start and end their design lifecycle without having to ask their supply chain team, their HR team, and their integration team to throw a king’s ransom at the problem. Transition the skunk works, apply EA to modernize your infrastructure on a achievable schedule may prove a tough challenge. Etarios can guide you with as much or as little help as you’d like. Please check out https://www.etairos.com to see what Etairos can do for you!

Previously, we told of the benefits our fellows in the semiconductor industry can harvest by adopting the principles of an Enterprise Architecture (EA) Program. We brought to light that – though the time and effort to fire up SemiConductor EA seems counter-productive – the fruits of a lowered infrastructure spend, as well as a leap forward in the race to tape out are the rewards. EA Programs are going to prove to the industry that those who step up will step away from the crowd.

The technology stack supporting design underpins this modern approach to super-computing and must abandon the stovepipe and the skunk-works. The narrow-minded architecture is costly. The holistic approach to High Performance Computing (HPC) design encompassing; storage, servers, virtualization, connectivity and cloud pushing up through the capture, design, simulation and verification applications needs to be established throughout the flow. An optimized stack yields the performance you want.

The benefits of enterprise-class technology may not be so obvious, but the value is quantified as consumption of the resources grows. As the demand grows, first step is often to eliminate slowdowns with immediate point solutions, which may not fit into an integrated EA topology. These short sighted solutions often solve department-centric challenges, yet these short-sighted answers result in higher costs overall. The real cost is support of the disparate systems, and effort to integrate.

All too often, a design firm’s EDA tools support team has the laborious job of maintaining several hundred integration patterns and the RTL developer is continually adding another nightly batch job – these end up being the tape and strapping wire that is cobbled together to create a synthetic alternative to an Enterprise-class environment. The environment starts to resemble a modern-day Rube Goldberg machine.

One example is we looked at a combination Semiconductor design/Analysis environment for a medical device manufacturer. Taking the holistic approach we shaved 40 % off the $ 3 million allocated budget, saved $ 550k in manpower costs and were able to increase analysis coverage by 20 %. So, as the industry pursues 10 nanometer solutions, those design firms that have tooled their compute environment effectively with an Enterprise-class topology will be the ones who will be able to start and end their design lifecycle without having to ask their supply chain team, their HR team, and their integration team to throw a king’s ransom at the problem. Transition the skunk works, apply EA to modernize your infrastructure on a achievable schedule may prove a tough challenge. Etarios can guide you with as much or as little help as you’d like. Please check out https://www.etairos.com to see what Etairos can do for you!